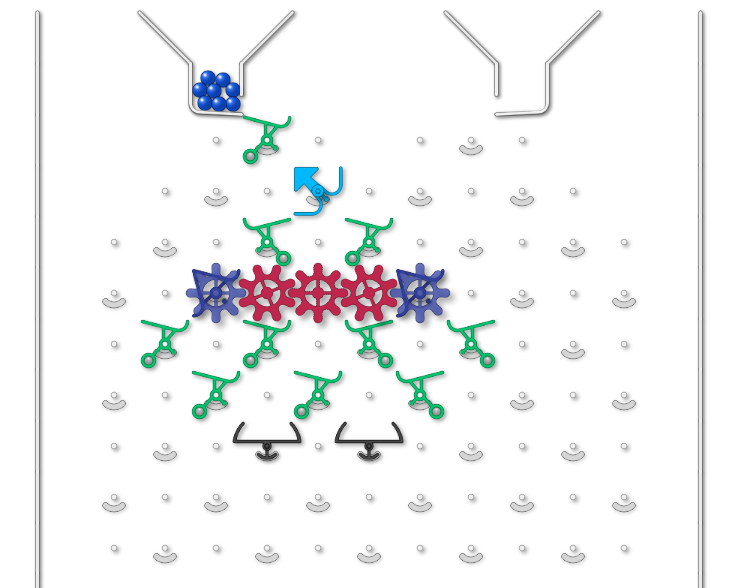

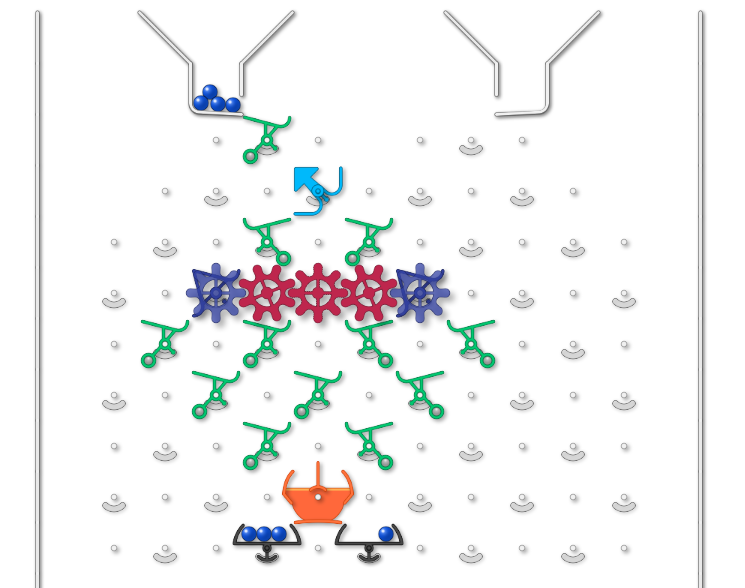

Here is a simple 2-input AND logic gate that you can share with students:

This was fun to create and refactor. Any other AND gate solutions?

Sorry - I should provide some context:

INPUTS

blue bit at top is INPUT A (left is 0, right is 1)

purple gear bit series below is INPUT B (left is 0, right is 1)

OUTPUT

black trap at bottom left represents 0

black trap at bottom right represents 1

TRUTH TABLE

A B Output

0 0 0

1 0 0

0 1 0

1 1 1